Vi skriver testbenchmodulet og kører simuleringen i ModelSim-miljøet fra Altera.

Nødvendig

- - computer;

- - installeret udviklingsmiljø Quartus II + ModelSim.

Instruktioner

Trin 1

Det første trin er at sikre, at stien til ModelSim-værktøjet er specificeret i Quartus II-udviklingsmiljøet. For at gøre dette skal du åbne menuen Funktioner -> Indstillinger. I indstillingerne skal du gå til Generelt -> EDA-værktøjsindstillinger. Vi finder ModelSim-Altera-feltet og skriver C: / altera / 13.0sp1 / modelsim_ase / win32aloem ind i det, eller ved at klikke på knappen med tre prikker ser vi efter denne mappe på vores computer. For en anden version af Quartus end min vil du naturligvis have din egen vej til "win32aloem" -mappen.

Trin 2

Du har et projekt til en FPGA i Quartus II. Sådan skriver du test eller testbænke (testbench) - dette er et emne for en separat artikel. Lad os nu antage, at din testbænk allerede er skrevet. Nu skal du fortælle udviklingsmiljøet, hvilken test du vil bruge, når du simulerer. For at gøre dette skal du åbne indstillingerne gennem menuen Opgaver -> Indstillinger … I vinduet, der åbnes, i sektionen EDA-værktøjsindstillinger -> Simulation, skal du klikke på knappen Testbænke … Her kan du forresten indstille flere tests og skift til den krævede, når projektet kompileres.

Trin 3

Et vindue til redigering af tests er åbnet. Vi har ikke oprettet nogen testbænke endnu, så listen er tom. Klik på knappen Ny … I det vindue, der åbnes, skal du indstille testindstillingerne.

Til venstre for feltet skal du klikke på knappen med tre prikker. Vælg filen med testbench-koden, og klik på Åbn. Klik nu på knappen Tilføj. Testen blev vist på listen over tests.

Derefter skal du i feltet indstille navnet på det topniveau-modul, der er defineret i din testbænk. Du kan indtaste ethvert navn i feltet, som standard oprettes det automatisk det samme som modulets navn.

Det er det, vi har indstillet de grundlæggende testindstillinger. Klik på OK to gange. Nu er vores test vist i rullelisten med testbænke. Klik på OK igen.

Trin 4

Hvis du ikke har foretaget syntesen af projektet endnu, er det tid til at gøre det. Vælg Behandling -> Start -> Start analyse og syntese i menuen, eller tryk på tastekombinationen Ctrl + K, eller klik blot på det tilsvarende ikon i toppanelet.

Trin 5

Simulation kan startes. Vælg Værktøjer -> Kør simuleringsværktøj -> RTL Simulation i menuen (1) eller klik på ikonet RTL Simulation i toppanelet (2).

Trin 6

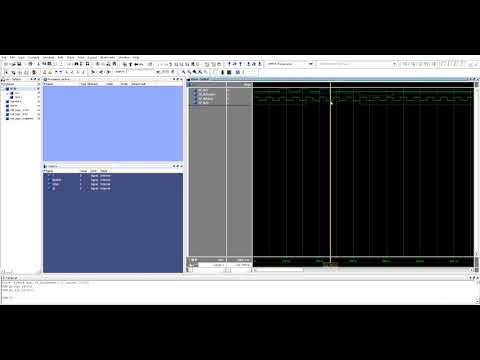

ModelSim-værktøjet starter, som udfører alle de instruktioner, der er skrevet i din testbænk, og stopper (hvis du specifikt har angivet dette med $ stop-direktivet i testkoden). Skærmen viser niveaudiagrammerne for FPGA input og output signaler, som du beskrev i dit projekt.